Among optocouplers, those providing the greatest thermal and time stability are those with two matched photodetectors in the package with the photoemitter. This configuration lets the deveice be used in a servo circuit. The current from one of the photodetectors (P1) is used to estimate the photocurrent that is delivered to the other photodetector (P2). The circuit placed around this device provides a drive current to the photoemitter which is servoed to be that which produces the desired current in P1, thus producing this same desired current in P2, to the matching accuracy of P1 and P2.

The Vishay IL300 analog optocoupler is a good example of such an optocoupler. Its data sheet www.vishay.com/poptocouplers/list/product-83622/ shows a servo circuit.

The linearity of this example circuit is given as only 0.01 percent, when the bias current to the photoemitter is 10 mA and the modulation on top of this is +-4 mA.

The drift with temperature of this example circuit is only +-0.005% per degree C typically, +-0.05% per degree C maximum. The data sheet shows the frequency response of the IL300 from photoemitter current to photodetector current is DC to 200 KHz (at 3 db rolloff, -45 degree phase delay).

The photodetector current / photoemitter current is typically 0.007 Using this ratio, the external circuit (op amp output to negative input) voltage gain is about (30,000 / 100) * 0.007 = about 2.

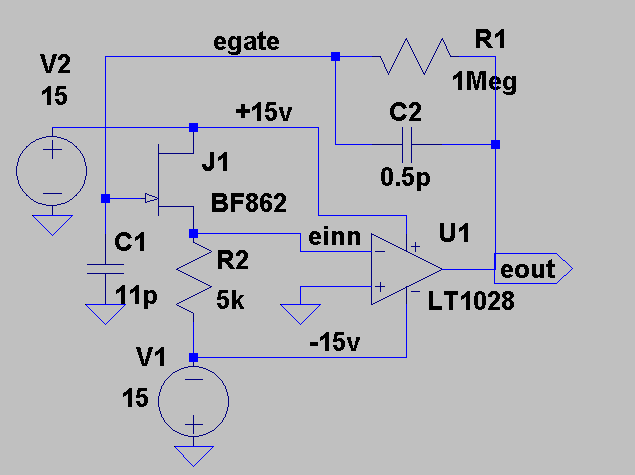

The example circuit (Fig. 13) uses a LM201 op amp with external compensation of 100 pf (between pins 1 and 8). This gives the op amp an open loop gain of 0.5 at about 300 KHz The total circuit’s open loop gain will trherefore be about 1 at 300 KHz.

The added phase lag from the photoemitter to photodetector response is 45 degrees at 200 KHz. So it will be somewhat more than this at 300 KHz., maybe 60 degrees.

The op amp’s open-loop phase lag at 300 MHz is about 90 degrees, so very roughly the total unity gain phase lag might be about 150 degrees. this is less than 180 degrees so the circuit should be stable but it should have quite a bit of square wave overshoot. My main point is one must design the servo circuit carefully. One must avoid instability due to phase lag in the photoemitter to photodetector path. Vishay has an app note 55: http://www.vishay.com/docs/83711/appn55.pdf showing in Fig. 6 that you can use a capacitor from the op amp out[put to the feedback input (the negative input) to achieve stability, by providing a non-phase-lagged feedback path for the higher frequencies.

When the right component values are used, keeping the feedback loop phase shift under about 120 degrees at the unity open-loop-gain frequency, the op amp in this case can be a unity-gain-stable op amp. Interestingly, however, in Fig. 6, the uncompensated OP-07 is used. I an skeptical of this curcuit as shown, because it does not have a dominant pole. I suspect that they just omitted an external compensating capacitor in the schematic.

As always, one should SPICE model the circuit. in particular, one can learn a lot from the servo’s open loop Bode plot. I like Liner Technology’s LTSpice for this purpose.

Your thoughts?

Larry Miller